Overview

COURSE DESCRIPTION

Upgrade VLSI’s physical design course is designed to give hands on experience in designing complex chip physical design from RTL to GDS by utilizing industry standard EDA tools. Course majorly focuses in improving student skill set from the basics and gradually introduce more complex topics with the help of industry standard live projects. Course material, hand-outs and regular assignments help student to get quick jobs in the semiconductor market. By end of the course you will learn all basics required for interview, physical design flow such from floorplanning, power planning, placement, clock tree synthesis and physical verification.

Upgrade VLSI is top 10 best physical design training institute in India for job oriented physical design training. Our trainers are 15+ years of experienced industry working professionals.

ELIGIBILITY

- B.E/B.Tech in EEE, ECE & EIE pursuing or completed.

- M.E/M.Tech/M.S in VLSI/Embedded/Any other specialization

MODE OF STUDY

- Available in Offline and Online modes.

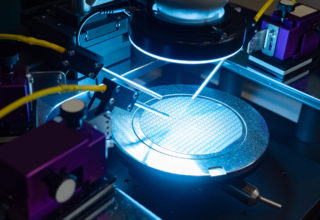

- Daily online classes conducted along with VPN based lab access.

LEARNING OUTCOMES

- Get hands-on experience in physical design from RTL to GDSII by executing industry standard live projects.

- Gain deep knowledge in chip design concepts such as floorplanning, power planning and building various type of clock trees.

- Acquire skill set in Static Timing Analysis and Synthesis.

- Learn to verify chip design using all physical verification concepts.

- Placement ready with improved softskills and digital basics.

KEY COURSE FEATURES

- 100% placement and tool support till placement is done.

- 24×7 tool access through vpn.

- Affordable fee and EMI facility.

- Industry live projects under the supervision of 15+ experienced trainer.

- Course material, hand-outs, quizzes, assignments to assist in learning.

Course Features

- Lectures 42

- Quizzes 0

- Duration 22 weeks

- Skill level Beginner

- Language English

- Students 20

- Assessments Yes

Curriculum

- Module 1: Basics of Unix/Linux

- Module 2: Basics of CMOS

- Module 3: Digital Electronics

- Module 4: Introduction to ASIC Design

- Module 5: Introduction to Verilog

- Module 6: Introduction to DFT

- Module 7: Synthesis

- Module 8: Static Timing Analysis Part – 1

- Module 9: Static Timing Analysis Part – 2

- Module 10: Physical Design

- Input files, Sanity Checks and IO placement Copy

- Floorplanning and Power planning concepts Copy

- Placement strategies like region, fence, blockages, pading, bump, dont touch, filler gap, DRV optimization, Buffer tree synthesis Copy

- Clock tree synthesis and clock latency calculations Copy

- Routing design and optimization, antenna Effect and Latch up issue Copy

- ECO Timing closure and implementation cycle Copy

- Module 11: Physical Design Verification

- Module 12: Industry standard Project Execution

- Module 13: Mock Interviews & Personality Improvement